## 1. CTPM interface to Host

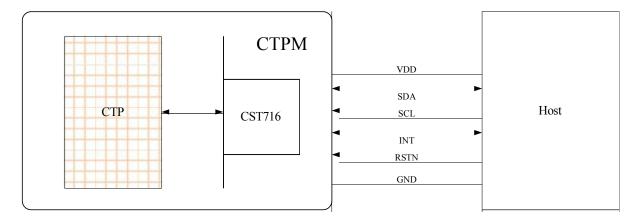

Figure 1-1 shows how CTPM communicates with host device. I<sub>2</sub>C interface supported by CSTx16 that is two-wire serial bus consisting of data line SDA and SCL clock line, used for serial data transferring between host and slave device.

Figure 1-1 CTPM and Host connection

INT port and RSTN port form the control interface. The INT port controlled by CST716 will send out an interrupt request signal to the host when there is a valid touch on CTP. The INT port also has another input function that host can wake up CST716 from the Hibernate mode. Host can send the reset signal to CTPM via RSTN port to reset the CST716 if needed. The Power Supply voltage of CTPM ranges from 2.7V to 3.6V. For details, please refer to Table 1-1.

**Description Port Name** VDD CTPM power supply, ranges from 2.7V to 3.6V. I<sub>2</sub>C data input and output. **SDA** I2C clock input. SCL The interrupt request signal from CTPM to Host. The wake up signal from host to CTPM, active low and the low pulse width INT ranges from 0.1ms to 1ms. The reset signal from host to CTPM, active low, and the low pulse width should **RSTN** be more than or equal to 1ms. **GND** Power ground.

Table 1-1 Description for CTPM and Host interface

## 1.1 I2C Read/Write Interface description

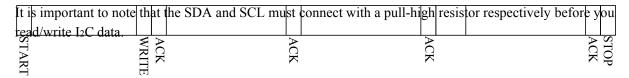

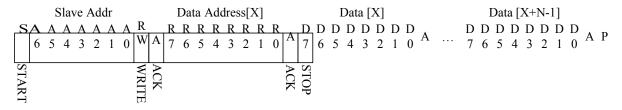

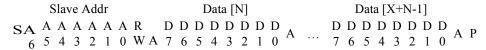

Write N bytes to I<sub>2</sub>C slave

Set Data Address

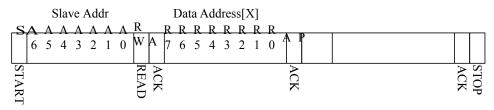

Read X bytes from I<sub>2</sub>C Slave

INT

## 1.2 Interrupt/Wake-up signal from CTPM to Host

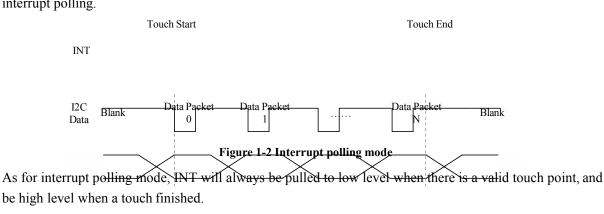

As for standard CTPM, host needs to use both interrupt signal and I<sub>2</sub>C interface to get the touch data. CTPM will output an interrupt request signal to the host when there is a valid touch. Then host can get the touch data via I<sub>2</sub>C interface. If there is no valid touch detected, the INT will output high level, and the host does not need to read the touch data. There are two kinds of method to use interrupt: interrupt trigger and interrupt polling.

Touch Start Touch End

I2C Blank Data Packet Data Packet Data Packet Data Packet Blank

Figure 1-3 Interrupt trigger mode

While for interrupt trigger mode, INT signal will be set to low if there is a touch detected. But whenever an update of valid touch data, CTPM will produce a valid pulse on INT port for INT signal, and host can read the touch data periodically according to the frequency of this pulse. In this mode, the pulse frequency is the touch data updating rate.

When CTPM stays in hibernate mode, the INT port will act as a pull-high input port and wait for an external wake up signal. Host may send out a low pulse to wake up CTPM from the hibernate mode. The wake-up low pulse width ranges from 0.5 ms to 1 ms, the reason for this is that the INT port will act as an interrupt request signal output port after wake-up.

#### 1.3 Reset signal from Host to CTPM

Host can send the reset signal via RSTN port to reset. The reset signal should not be set to low while in normal running mode, but when programming flash, the RSTN port must be connected to GND. The RSTN port can also be used to active the CTPM in hibernate mode. Note that the reset pulse width should be more than 1ms.

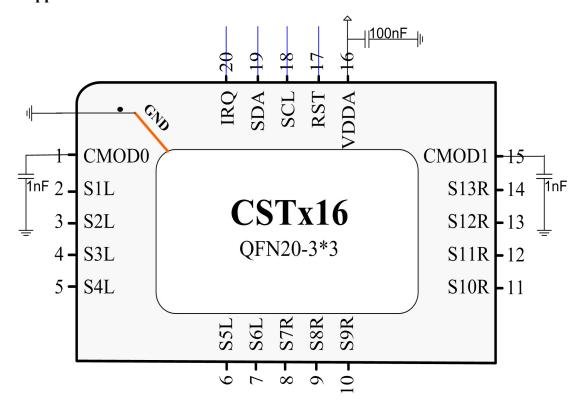

## 2. Standard Application circuit of

Table 2-1 is a brief summary of application features. Figure 2-1, Figure 2-2, demonstrates the typical application schematic.

IC Type

CST716

Operating Voltage(V)

2.6 ~ 3.6

Channel

13

Touch points

2

Interface

I2C

Report rate

>50Hz

Package (mm)

3\*3 QFN20

**Table 2-1 Brief features**

# 2.1 application schematic

# 3. CTPM Register Mapping

This chapter describes the standard CTPM communication registers in address order for working mode. The most detailed descriptions of the standard products communication registers are in the register definitions section of each chapter.

## 3.1 Working Mode

The CTP is fully functional as a touch screen controller in working mode. The access address to read and write is just logical address which is not enforced by hardware or firmware. Here is the working mode register map.

## Working Mode Register Map

| Address | Name      | Default<br>Value | Bit7            | Bit6                                   | Bit5    | Bit4    | Bit3         | Bit2                            | Bit1     | Bit0 | Host<br>Access |

|---------|-----------|------------------|-----------------|----------------------------------------|---------|---------|--------------|---------------------------------|----------|------|----------------|

| 0x00    | DEV MODE  | 0x00             |                 |                                        |         |         |              |                                 |          |      | R              |

|         | GEST ID   |                  | A 1             | · 0                                    |         |         |              |                                 |          |      |                |

| 0x01    | GEST_ID   | 0x00             | Alwa            | iys u                                  |         |         | F0 07:       |                                 |          |      | R              |

| 0x02    | TD_STATUS | 0x00             |                 |                                        |         |         | [3:0] points | Numbe<br>s                      | r of tou | ch   | R              |

| 0x03    | P1_XH     | 0xFF             | [7:6]1<br>Event |                                        |         |         |              | 1st Touc<br>sition[1            |          |      | R              |

| 0x04    | P1_XL     | 0xFF             | [7:0]           | 1st Touc                               | ch X Po | sition  |              |                                 |          |      | R              |

| 0x05    | P1_YH     | 0xFF             | [7:4]           | 1st Touc                               | ch ID   |         |              | 1st Toucition[1                 |          |      | R              |

| 0x06    | P1 YL     | 0xFF             | [7:0]           | [7:0] 1st Touch Y Position             |         |         | R            |                                 |          |      |                |

| 0x07    | P1_WEIGHT | 0xFF             | [7:0]           | 1 <sub>st</sub> Touc                   | h Weig  | ht      |              |                                 |          |      | R              |

| 0x08    | P1_MISC   | 0xFF             | [7:4]           | 1st Touc                               | h Area  |         |              |                                 |          |      | R              |

| 0x09    | P2_XH     | 0xFF             | [7:6]2<br>Event |                                        |         |         |              | 2nd Touc<br>sition[1            |          |      | R              |

| 0x0A    | P2_XL     | 0xFF             | [7:0]           | 2nd Tou                                | ch X Po | osition |              |                                 |          |      | R              |

| 0x0B    | P2_YH     | 0xFF             | [7:4]           | 2ndTouc                                | ch ID   |         |              | 2 <sub>nd</sub> Tou<br>ition[1] |          |      | R              |

| 0x0C    | P2_YL     | 0xFF             | [7:0]           | [7:0] 2 <sub>nd</sub> Touch Y Position |         |         |              | R                               |          |      |                |

| 0x0D    | P2_WEIGHT | 0xFF             | [7:0]           | 2nd Tou                                | ch Weig | ght     |              |                                 |          |      | R              |

| 0x0E    | P2_MISC   | 0xFF             | [7:4]           | 2nd Tou                                | ch Area | ı       |              |                                 |          |      | R              |

|         |           |                  |                 |                                        |         |         |              |                                 |          |      |                |

| 0xA5    | PWR_MODE  | 0x00             | [7:0]           | Current                                | power   | mode    | which s      | ystem i                         | is in    |      | R/W            |

## 3.1.1 DEVICE MODE

Always 0

## **3.1.2 GEST\_ID**

Always 0

## 3.1.3 TD STATUS

This register is the Touch Data status register.

| Address  | Bit Address | Register Name                | Description                              |  |

|----------|-------------|------------------------------|------------------------------------------|--|

| 0x02 3:0 |             | Number of touch points [3:0] | The detected point number, 1-2 is valid. |  |

| 0.02     | 7:4         | Reserved                     |                                          |  |

## 3.1.4 Pn\_XH (n:1-2)

This register describes MSB of the X coordinate of the nth touch point and the corresponding event flag.

| Ad | dress    | Bit Address | Register Name | Description                     |

|----|----------|-------------|---------------|---------------------------------|

|    | x03<br>~ | 7:6         | Event Flag    | 00b: Press Down<br>01b: Lift Up |

| 0x09 |     |                         | 10b: Contact                      |

|------|-----|-------------------------|-----------------------------------|

|      |     |                         | 11b: No event                     |

|      | 5:4 |                         | Reserved                          |

|      | 3:0 | Touch X Position [11:8] | MSB of Touch X Position in pixels |

## 3.1.5 Pn XL (n:1-2)

This register describes LSB of the X coordinate of the nth touch point.

| Address | Bit Address | Register Name          | Description                           |

|---------|-------------|------------------------|---------------------------------------|

| 0x04    |             |                        |                                       |

| ~       | 7:0         | Touch X Position [7:0] | LSB of the Touch X Position in pixels |

| 0x0A    |             |                        | -                                     |

## 3.1.6 Pn\_YH (n:1-2)

This register describes MSB of the Y coordinate of the nth touch point and corresponding touch ID.

| Address | Bit Address | Register Name           | Description                                      |

|---------|-------------|-------------------------|--------------------------------------------------|

| 0x05    | 7:4         | Touch ID[2:0]           | Touch ID of Touch Point, this value is 0x0F when |

| ~       | 7.4         | Touch ID[3:0]           | the ID is invalid                                |

| 0x0B    | 3:0         | Touch Y Position [11:8] | MSB of Touch Y Position in pixels                |

## 3.1.7 Pn\_YL (n:1-2)

This register describes LSB of the Y coordinate of the nth touch point.

| Address | Bit Address | Register Name          | Description                           |

|---------|-------------|------------------------|---------------------------------------|

| 0x06    |             |                        |                                       |

| ~       | 7:0         | Touch Y Position [7:0] | LSB of the Touch Y Position in pixels |

| 0x0C    |             |                        | _                                     |

## 3.1.8 Pn WEIGHT (n:1-2)

This register describes weight of the nth touch point.

| Address | Bit Address | Register Name     | Description          |

|---------|-------------|-------------------|----------------------|

| 0x07    |             |                   |                      |

| ~       | 7:0         | Touch Weight[7:0] | Touch pressure value |

| 0x0D    |             |                   |                      |

## 3.1.9 Pn MISC (n:1-2)

This register describes the miscellaneous information of the nth touch point.

|         |             |                 | 1                |

|---------|-------------|-----------------|------------------|

| Address | Bit Address | Register Name   | Description      |

| 0x08    |             |                 |                  |

| ~       | 7:4         | Touch Area[3:0] | Touch area value |

| 0x0E    |             |                 |                  |

# 3.1.10 PWR\_MODE

Control TP power mode

0x00: active mode

0x03: sleep mode, need pull low reset pin to wake up TP

## 4. Communication between host and CTPM

ucBufLen - length of buffer

#### 4.1 Communication Contents

The data Host received from the CTPM through I<sub>2</sub>C interface are different depend on the configuration in Device Mode Register of the CTPM. Please refer to Section 3---CTPM Register Mapping.

## 4.2 I<sub>2</sub>C Example Code

//

```

void i2cBurstWriteBytes(BYTE ucSlaveAdr, BYTE ucSubAdr, BYTE *pBuf, BYTE ucBufLen)

BYTE ucDummy; // loop dummy

ucDummy = I2C ACCESS DUMMY TIME;

while(ucDummy--)

if (i2c_AccessStart(ucSlaveAdr, I2C_WRITE) == FALSE)

continue;

if (i2c SendByte(ucSubAdr) == I2C NON ACKNOWLEDGE) // check non-acknowledge

continue;

while(ucBufLen--) // loop of writting data

i2c_SendByte(*pBuf); // send byte

pBuf++; // next byte pointer

} // while

break; }

// while

i2c Stop();

}

// I2C read bytes from device.

//

// Arguments: ucSlaveAdr - slave address

//

ucSubAdr - sub addres

//

pBuf - pointer of buffer

//

ucBufLen - length of buffer

void i2cBurstReadBytes(BYTE ucSlaveAdr, BYTE ucSubAdr, BYTE *pBuf, BYTE ucBufLen)

BYTE ucDummy; // loop dummy

ucDummy = I2C_ACCESS_DUMMY_TIME;

while(ucDummy--)

if (i2c AccessStart(ucSlaveAdr, I2C WRITE) == FALSE)

continue;

if (i2c_SendByte(ucSubAdr) == I2C_NON_ACKNOWLEDGE) // check non-acknowledge

continue;

if (i2c_AccessStart(ucSlaveAdr, I2C_READ) == FALSE)

continue;

while(ucBufLen--) // loop to burst read

{

*pBuf = i2c_ReceiveByte(ucBufLen); // receive byte

pBuf++; // next byte pointer

} // while

break;

} // while

i2c_Stop();

}

```

```

// I2C read current bytes from device.

// Arguments: ucSlaveAdr - slave address

//

pBuf - pointer of buffer

//

ucBufLen - length of buffer

void i2cBurstCurrentBytes(BYTE ucSlaveAdr, BYTE *pBuf, BYTE ucBufLen)

{

BYTE ucDummy; // loop dummy

ucDummy = I2C ACCESS DUMMY TIME;

while(ucDummy--)

if (i2c_AccessStart(ucSlaveAdr, I2C_READ) == FALSE)

continue;

while(ucBufLen--) // loop to burst read

*pBuf = i2c_ReceiveByte(ucBufLen); // receive byte

pBuf++; // next byte pointer

} // while

break;

} // while

i2c_Stop();

}

```